### **CLC030**

# SMPTE 292M/259M Digital Video Serializer with Video and Ancillary Data FIFOs and Integrated Cable Driver

### **General Description**

The CLC030 SMPTE 292M/259M Digital Video Serializer with Ancillary Data FIFO and Integrated Cable Driver is a monolithic integrated circuit that encodes, serializes and transmits bit-parallel digital video data conforming to SMPTE 125M and 267M standard definition, 10-bit wide component video and SMPTE 260M, 274M, 295M and 296M high-definition, 20-bit wide component video standards. The CLC030 operates at SMPTE 259M serial data rates of 270 Mbps, 360 Mbps, the SMPTE 344M serial data rate of 540 Mbps; and the SMPTE 292M serial data rates of 1483.5 and 1.485 Gbps. The serial data clock frequency is internally generated and requires no external frequency setting, trimming or filtering components.

The CLC030 performs functions which include: parallel-toserial data conversion, SMPTE standard data encoding, NRZ to NRZI data format conversion, serial data clock generation and encoding with the serial data, automatic video rate and format detection, ancillary data packet management and insertion, and serial data output driving. The CLC030 has circuitry for automatic EDH/CRC character and flag generation and insertion per SMPTE RP-165 (standard definition) or SMPTE 292M (high definition). Optional LSB dithering is implemented which prevents pathological pattern generation. Unique to the CLC030 are its video and ancillary data FIFOs. The video FIFO allows the video data to be delayed from 0 to 4 parallel data clock periods for video timing purposes. The ancillary data port and on-chip FIFO and control circuitry store and insert ancillary flags, data packets and checksums into the ancillary data space. The CLC030 also has an exclusive built-in self-test (BIST) and video test pattern generator (TPG) with SD and HD component video test patterns: reference black, PLL and EQ pathologicals and color bars in 4:3 and 16:9 raster formats for NTSC and PAL standards\*. The color bar patterns feature optional bandwidth limiting coding in the chroma and luma

The CLC030 has a unique multi-function I/O port for immediate access to control and configuration settings. This port may be programmed to provide external access to control functions and indicators as inputs and outputs. The designer can thus customize the CLC030 to fit the desired application. At power-up or after a reset command, the CLC030 is autoconfigured to a default operating condition. Separate power pins for the output driver, PLL and the serializer improve power supply rejection, output jitter and noise performance.

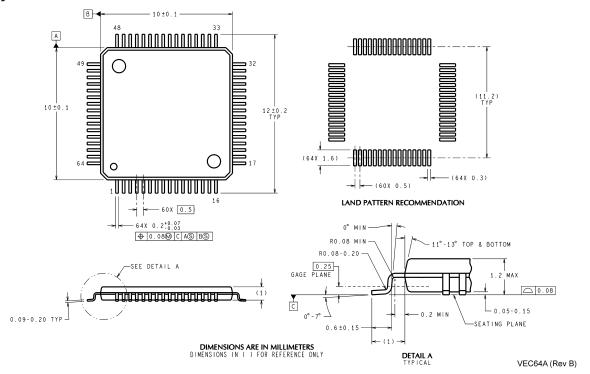

The CLC030's internal circuitry is powered from +2.5V and the I/O circuitry from a +3.3V supply. Power dissipation is typically 430mW at 1.485Gbps including two 75 $\Omega$  ACcoupled and back-matched output loads. The device is packaged in a 64-pin TQFP.

#### **Features**

- SDTV/HDTV serial digital video standard compliant

- Supports 270 Mbps, 360 Mbps, 540 Mbps, 1.4835Gbps and 1.485 Gbps SDV data rates with auto-detection

- LSB dithering option

- No external serial data rate setting or VCO filtering components required\*

- Fast PLL lock time: < 150µs typical at 1.485 Gbps

- Adjustable depth video FIFO for timing alignment

- Built-in self-test (BIST) and video test pattern generator (TPG)\*

- Automatic EDH/CRC word and flag generation and insertion

- On-chip ancillary data FIFO and insertion control circuitry

- Flexible control and configuration I/O port

- LVCMOS compatible data and control inputs and outputs

- 75Ω ECL-compatible, differential, serial cable-driver outputs

- 3.3V I/O power supply, 2.5V logic power supply operation

- Low power: typically 430mW

- 64-pin TQFP package

- Commercial temperature range 0°C to +70°C

- \* Patent applications made or pending.

### **Applications**

- SDTV/HDTV parallel-to-serial digital video interfaces for:

- Video cameras

- VTRs

- Telecines

- Digital video routers and switchers

- Digital video processing and editing equipment

- Video test pattern generators and digital video test equipment

- Video signal generators

| Order Number CLC030VEC | 64-Pin TQFP | NS Package Number VEC-64A |

|------------------------|-------------|---------------------------|

|------------------------|-------------|---------------------------|

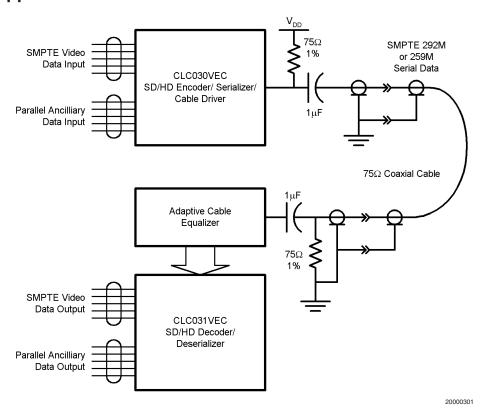

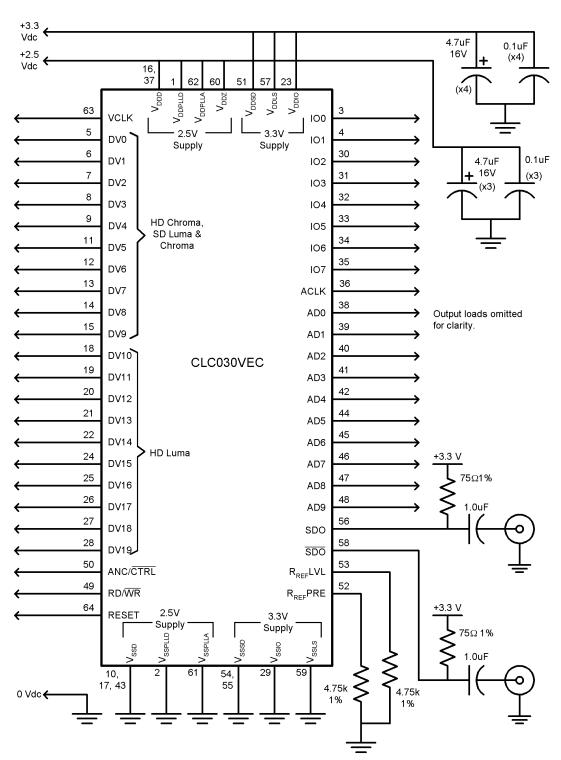

# **Typical Application**

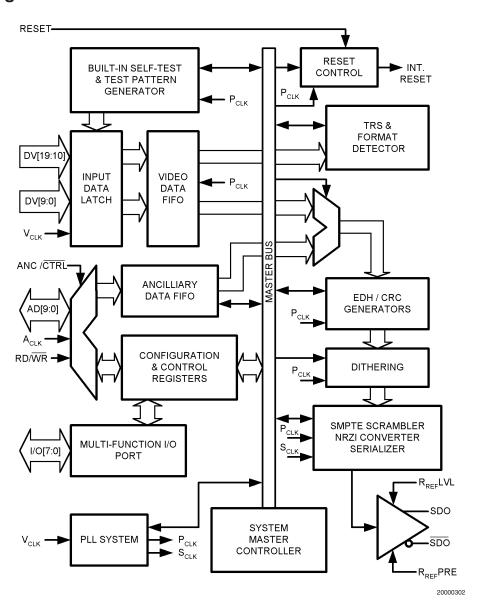

# **Block Diagram**

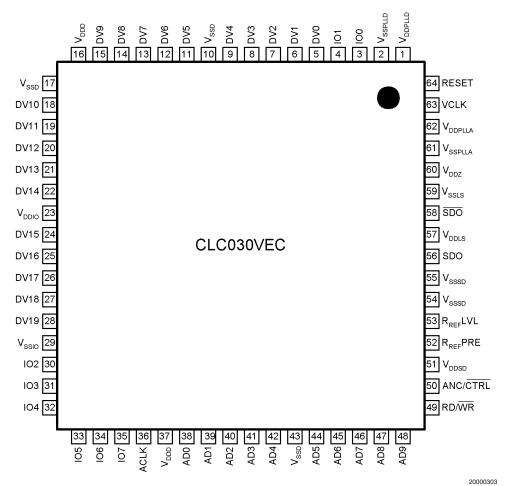

## **Connection Diagram**

64-Pin TQFP Order Number CLC030VEC See NS Package Number VEC-64A

| Absolute Waximum Ratings (Note 1) It                             |

|------------------------------------------------------------------|

| is anticipated that this device will not be offered in a         |

| military qualified version. If Military/Aerospace specified      |

| devices are required, please contact the National Semicon-       |

| ductor Sales Office / Distributors for availability and specifi- |

| cations.                                                         |

| Cations.                                       |                          |

|------------------------------------------------|--------------------------|

| CMOS I/O Supply Voltage                        |                          |

| $(V_{DDIO}-V_{SSIO})$ :                        | 4.0V                     |

| SDO Supply Voltage                             |                          |

| $(V_{DDSD}-V_{SSSD})$ :                        | 4.0V                     |

| Digital Logic Supply Voltage                   |                          |

| $(V_{DDD}-V_{SSD})$ :                          | 3.0V                     |

| PLL Digital Supply Voltage                     |                          |

| (V <sub>DDPLL</sub> -V <sub>SSPLL</sub> ):     | 3.0V                     |

| PLL Analog Supply Voltage                      |                          |

| $(V_{DDPLLA}-V_{SSPLLA}), (V_{DDZ}-V_{SSD})$ : | 3.0V                     |

| CMOS Input Voltage                             | $V_{\rm SSIO}$ –0.15V to |

| (Vi):                                          | $V_{DDIO} + 0.15V$       |

|                                                |                          |

| CMOS Output Voltage                     | $V_{\rm SSIO}$ –0.15V to |

|-----------------------------------------|--------------------------|

| (Vo):                                   | $V_{DDIO}$ +0.15V        |

| CMOS Input Current (single input):      |                          |

| $Vi = V_{SSIO} -0.15V$ :                | −5 mA                    |

| $Vi = V_{DDIO} + 0.15V$ :               | +5 mA                    |

| CMOS Output Source/Sink Current:        | ±10 mA                   |

| SDO Output Sink Current:                | 40 mA                    |

| Package Thermal Resistance              |                          |

| $\theta_{JA}$ @ 0 LFM Airflow           | 47°C/W                   |

| $\theta_{JA} \ @ \ 500 \ LFM \ Airflow$ | 27°C/W                   |

| $	heta_{\sf JC}$                        | 6.5°C/W                  |

| Storage Temp. Range:                    | -65°C to +150°C          |

| Junction Temperature:                   | +150°C                   |

| Lead Temperature (Soldering 4 Sec):     | +260°C                   |

| ESD Rating (HBM):                       | 2 kV                     |

| ESD Rating (MM):                        | 250V                     |

|                                         |                          |

# **Recommended Operating Conditions**

| Symbol             | Parameter                         | Conditions                             | Reference        | Min               | Тур   | Max        | Units             |

|--------------------|-----------------------------------|----------------------------------------|------------------|-------------------|-------|------------|-------------------|

| $V_{\rm DDIO}$     | CMOS I/O Supply Voltage           | V <sub>DDIO</sub> -V <sub>SSIO</sub>   |                  | 3.150             | 3.300 | 3.450      | V                 |

| V <sub>DDSD</sub>  | SDO Supply Voltage                | V <sub>DDSD</sub> -V <sub>SSSD</sub>   |                  | 3.150             | 3.300 | 3.450      | V                 |

| V <sub>DDD</sub>   | Digital Logic Supply<br>Voltage   | $V_{DDD}$ - $V_{SSD}$                  |                  | 2.375             | 2.500 | 2.625      | V                 |

| V <sub>DDPLL</sub> | PLL Supply Voltage                | V <sub>DDPLL</sub> -V <sub>SSPLL</sub> |                  | 2.375             | 2.500 | 2.625      | V                 |

| $V_{DDZ}$          | Analog Supply Voltage             | V <sub>DDZ</sub> -V <sub>SSD</sub>     |                  | 2.375             | 2.500 | 2.625      | V                 |

| V <sub>IL</sub>    | CMOS Input Voltage, Low<br>Level  |                                        |                  | V <sub>SSIO</sub> |       |            | V                 |

| V <sub>IH</sub>    | CMOS Input Voltage High<br>Level  |                                        |                  |                   |       | $V_{DDIO}$ | V                 |

| T <sub>A</sub>     | Operating Free Air<br>Temperature |                                        |                  | 0                 |       | +70        | °C                |

| t <sub>JIT</sub>   | Video Clock Jitter                |                                        | V <sub>CLK</sub> |                   | 30    |            | ps <sub>P-P</sub> |

### **DC Electrical Characteristics**

Over Supply Voltage and Operating Temperature ranges, unless otherwise specified (Notes 2, 3).

| Symbol                 | Parameter                                   | Conditions                                                                                       | Reference                             | Min               | Тур                       | Max                        | Units             |

|------------------------|---------------------------------------------|--------------------------------------------------------------------------------------------------|---------------------------------------|-------------------|---------------------------|----------------------------|-------------------|

| V <sub>IH</sub>        | Input Voltage High Level                    |                                                                                                  | All LVCMOS                            | 2.0               |                           | $V_{DDIO}$                 | V                 |

| V <sub>IL</sub>        | Input Voltage Low Level                     |                                                                                                  | Inputs                                | V <sub>SSIO</sub> |                           | 0.8                        | V                 |

| I <sub>IH</sub>        | Input Current High Level                    | $V_{IH} = V_{DDIO}$                                                                              |                                       |                   | +90                       | +150                       | μA                |

| I <sub>IL</sub>        | Input Current Low Level                     | V <sub>IL</sub> = V <sub>SSIO</sub>                                                              |                                       |                   | -1                        | -20                        | μA                |

| V <sub>OH</sub>        | CMOS Output Voltage<br>High Level           | $I_{OH} = -6.6 \text{ mA}$                                                                       | All LVCMOS<br>Outputs                 | 2.4               | 2.7                       | V <sub>DDIO</sub>          | V                 |

| V <sub>OL</sub>        | CMOS Output Voltage<br>Low Level            | I <sub>OL</sub> = +6.6 mA                                                                        |                                       | V <sub>SSIO</sub> | V <sub>SSIO</sub><br>+0.3 | V <sub>SSIO</sub><br>+0.5V | V                 |

| V <sub>SDO</sub>       | Serial Driver Output<br>Voltage             | Test Circuit, Test Loads<br>Shall Apply                                                          | SDO, SDO                              | 720               | 800                       | 880                        | mV <sub>P-P</sub> |

| I <sub>DD</sub> (3.3V) | Power Supply Current,<br>3.3V Supply, Total | V <sub>CLK</sub> = 27 MHz, NTSC<br>color Bar Pattern, Test<br>Circuit, Test Loads Shall<br>Apply | V <sub>DDIO</sub> , V <sub>DDSD</sub> |                   | 48                        | 65                         | mA                |

### DC Electrical Characteristics (Continued)

Over Supply Voltage and Operating Temperature ranges, unless otherwise specified (Notes 2, 3).

| Symbol                 | Parameter                                   | Conditions                                                                                          | Reference                        | Min | Тур | Max | Units |

|------------------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------------------|-----|-----|-----|-------|

| I <sub>DD</sub> (3.3V) | Power Supply Current,<br>3.3V Supply, Total | V <sub>CLK</sub> = 74.25 MHz, NTSC color Bar Pattern, Test Circuit, Test Loads Shall Apply          | $V_{DDIO}, V_{DDSD}$             |     | 66  | 90  | mA    |

| I <sub>DD</sub> (2.5V) | Power Supply Current,<br>2.5V Supply, Total | V <sub>CLK</sub> = 27 MHz, NTSC<br>color Bar Pattern, Test<br>Circuit, Test Loads Shall<br>Apply    | $V_{DDD}, V_{DDZ}, \\ V_{DDPLL}$ |     | 66  | 85  | mA    |

| I <sub>DD</sub> (2.5V) | Power Supply Current,<br>2.5V Supply, Total | V <sub>CLK</sub> = 74.25 MHz, NTSC<br>color Bar Pattern, Test<br>Circuit, Test Loads Shall<br>Apply | $V_{DDD}, V_{DDZ}, \\ V_{DDPLL}$ | 8:  |     | 110 | mA    |

#### **AC Electrical Characteristics**

Over Supply Voltage and Operating Temperature ranges, unless otherwise specified (Note 3).

| Symbol                          | Parameter                                    | Conditions                                | Reference                               | Min | Тур | Max              | Units             |

|---------------------------------|----------------------------------------------|-------------------------------------------|-----------------------------------------|-----|-----|------------------|-------------------|

| f <sub>VCLK</sub>               | Parallel Video Clock<br>Frequency            |                                           | V <sub>CLK</sub>                        | 27  |     | 74.25            | MHz               |

| DC <sub>V</sub>                 | Video Clock Duty<br>Cycle                    |                                           | V <sub>CLK</sub>                        | 45  | 50  | 55               | %                 |

| f <sub>ACLK</sub>               | Ancillary Clock<br>Frequency                 |                                           | A <sub>CLK</sub>                        |     |     | V <sub>CLK</sub> | MHz               |

| DC <sub>A</sub>                 | Ancillary Clock Duty<br>Cycle                |                                           | A <sub>CLK</sub>                        | 45  | 50  | 55               | %                 |

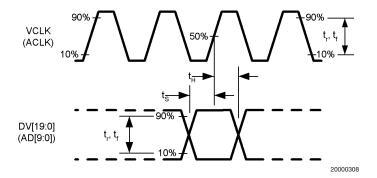

| t <sub>r</sub> , t <sub>f</sub> | Input Clock and Data<br>Rise Time, Fall Time | 10%–90%                                   | $V_{CLK}$ , $A_{CLK}$ , $DV_N$ , $AD_N$ | 1.0 | 1.5 | 3.0              | ns                |

| BR <sub>SDO</sub>               | Serial Data Rate                             | (Notes 5, 6)                              | SDO, SDO                                | 270 |     | 1,485            | M <sub>bps</sub>  |

| t <sub>r</sub> , t <sub>f</sub> | Rise Time, Fall Time                         | 20%-80%, (Note 6)                         | SDO, SDO                                |     |     | 270              | ps                |

| t <sub>r</sub> , t <sub>f</sub> | Rise Time, Fall Time                         | 20%-80%, (Note 5)                         | SDO, SDO                                |     | 500 |                  | ps                |

|                                 | Output Overshoot                             | (Note 4)                                  | SDO, SDO                                |     | 5   |                  | %                 |

| t <sub>j</sub>                  | Serial Output Jitter,<br>Intrinsic           | 270 M <sub>bps</sub> , (Notes 5, 9, 10)   | SDO, SDO                                |     | 200 |                  | ps <sub>P-P</sub> |

| t <sub>j</sub>                  | Serial Output Jitter,<br>Intrinsic           | 1,485 M <sub>bps</sub> , (Notes 6, 9, 10) | SDO, SDO                                |     | 120 |                  | ps <sub>P-P</sub> |

| t <sub>LOCK</sub>               | Lock Time                                    | (Notes 5, 7) (SD Rates)                   |                                         |     | 15  |                  | ms                |

| t <sub>LOCK</sub>               | Lock Time                                    | (Notes 6, 7) (HD Rates)                   |                                         |     | 15  |                  | ms                |

| t <sub>S</sub>                  | Setup Time, Video<br>Data                    | Timing Diagram, (Note 4)                  | DV <sub>N</sub> to V <sub>CLK</sub>     |     | 1.5 | 2.0              | ns                |

| t <sub>H</sub>                  | Hold Time, Video Data                        | Timing Diagram, (Note 4)                  | V <sub>CLK</sub> to DV <sub>N</sub>     |     | 1.5 | 2.0              | ns                |

| t <sub>S</sub>                  | Setup Time, Anc. Data<br>Port                | Timing Diagram, (Note 4)                  | AD <sub>N</sub> to A <sub>CLK</sub>     |     | 1.5 | 2.0              | ns                |

| t <sub>H</sub>                  | Hold Time, Anc. Data<br>Port                 | Timing Diagram, (Note 4)                  | A <sub>CLK</sub> to AD <sub>N</sub>     |     | 1.5 | 2.0              | ns                |

**Note 1:** "Absolute Maximum Ratings" are those parameter values beyond which the life and operation of the device cannot be guaranteed. The stating herein of these maximums shall not be construed to imply that the device can or should be operated at or beyond these values. The table of "Electrical Characteristics" specifies acceptable device operating conditions.

- Note 2: Current flow into device pins is defined as positive. Current flow out of device pins is defined as negative. All voltages are referenced to V<sub>SS</sub> = 0V.

- Note 3: Typical values are stated for  $V_{DDIO} = V_{DDSD} = +3.3V$ ,  $V_{DDD} = V_{DDPLL} = +2.5V$  and  $T_A = +25^{\circ}C$ .

- Note 4: Spec. is guaranteed by design.

- Note 5:  $R_L = 75\Omega$ , AC-coupled @ 270  $M_{bps}$ ,  $R_{REF}LVL = R_{REF}PRE = 4.75 k\Omega$  1%, See Test Loads and Test Circuit.

- $\textbf{Note 6:} \ \ R_L = 75\Omega, \ AC\text{-coupled} \ @ \ 1,485 \ M_{bps}, \ R_{REF}LVL = R_{REF}PRE = 4.75 \ k\Omega \ 1\%, \ See \ \textbf{Test Loads} \ and \ \textbf{Test Circuit}.$

- Note 7: Measured from rising-edge of first DV<sub>CLK</sub> cycle until Lock Detect output goes high (true). Lock time includes format detection time plus PLL lock time.

### AC Electrical Characteristics (Continued)

Note 8: Average value measured between rising edges computed over at least one video field.

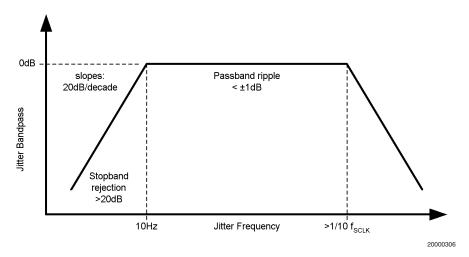

Note 9: Intrinsic timing jitter is measured in accordance with SMPTE RP 184-1996, SMPTE RP 192-1996 and the applicable serial data transmission standard, SMPTE 259M-1997 or SMPTE 292M (proposed). A color bar test pattern is used. The value of f<sub>SCLK</sub> is 270 MHz or 360 MHz for SMPTE 259M, 540MHz for SMPTE 344M or 1,485 MHz for SMPTE 292M serial data rates. See **Timing Jitter Bandpass** section.

Note 10: Intrinsic jitter is defined in accordance with SMPTE RP 184-1996 as: jitter at an equipment output in the absence of input jitter. As applied to this device, the input port is V<sub>CLK</sub> and the output port is SDO or SDO.

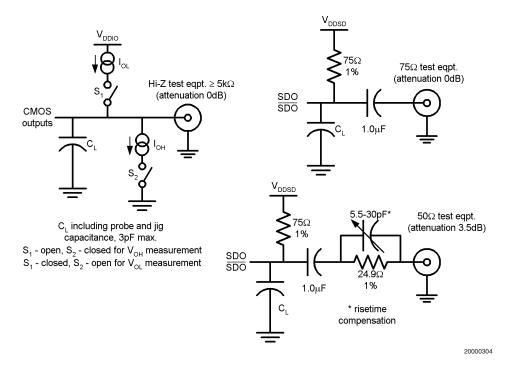

#### **Test Loads**

### **Timing Jitter Bandpass**

7

### **Test Circuit**

### **Timing Diagram**

### **Device Operation**

The CLC030 SDTV/HDTV Serializer is used in digital video signal origination equipment: cameras, video tape recorders, telecines and video test and other equipment. It converts parallel SDTV or HDTV component digital video signals into serial format. Logic levels within this equipment are normally produced by LVCMOS logic devices. The encoder produces serial digital video (SDV) signals conforming to SMPTE 259M, SMPTE 344M (proposed) or SMPTE 292M. The CLC030 operates at parallel data rates of 27.0 MHz, 36.0 MHz, 54.0 MHz, 74.176MHz and 74.25 MHz. Corresponding serial data rates are 270 Mbps, 360 Mbps, 540 Mbps, 1.4835Gbps and 1.485 Gbps.

#### **VIDEO DATA PATH**

The input data register accepts 10-bit standard definition or 20-bit high definition parallel data and associated parallel clock signals having LVCMOS-compatible levels. All parallel video data inputs, DV[19:0], have internal pull-down devices. VCLK does not have an internal pull-down device. Parallel video data may conform to any of several SMPTE standards: 125M, 267M, 260M, 274M, 295M or 296M. Some segmented frame formats are not supported. For HDTV data, the upper 10 bits of the DV input are luminance (luma) information and the lower 10 bits are color difference (chrominance or chroma) information. For SDTV data, the lower order 10 bits contain both luma and chroma information. Output from this register feeds the video FIFO, video format detection circuit, TRS character detector, SMPTE scrambler, EDH/CRC generators, serializer/NRZI converter and the device control system.

Data from the input data register passes into a 4-register deep **video FIFO** prior to encoding and other processing. The depth of this FIFO is set by the **VIDEO FIFO Depth[2:0]** bits of the **ANC 0** control register.

The **video format detector** automatically determines the raster characteristics (video data format) of the parallel input data and configures the CLC030 to properly handle the data. This assures that the data will be properly formatted, that the correct data rate is selected and that ancillary data, line numbers (HD) and CRC/EDH data are correctly inserted. Indication of the standard being processed is stored in the **FORMAT[4:0]** bits in the **FORMAT 1** control data register. This format data can be programmed for output on the multi-function I/O port.

The CLC030 normally operates in an auto-format-detection mode. It may optionally be configured to process only a single video format by writing the appropriate **FORMAT SET[4:0]** control data into the **FORMAT 0** control register. The default state of **FORMAT SET[4:0]** is 0000b. Also, the

CLC030 may be configured to handle only the standard-definition data formats by setting the SD ONLY bit or only the high-definition data formats by setting the HD ONLY bit in the FORMAT 0 control register. When both of these bits are reset the part automatically selects the data rate.

The TRS character detector processes the timing reference signals which control raster framing. The TRS detector supplies control signals to the system controller to identify the presence of the valid video data. The system controller supplies necessary control signals to the EDH/CRC control block. TRS character LSB-clipping as prescribed in ITU-R BT.601 is used. LSB-clipping causes all TRS characters with a value between 000h and 003h to be forced to 000h and all TRS characters with a value between 3FCh and 3FFh to be forced to 3FFh. Clipping is done prior to scrambling and EDH/CRC character generation.

The CLC030 incorporates circuitry for LSB dithering. The Dither Enable bit in the VIDEO INFO 0 register when set enables dithering. The V Dither Enable bit in the VIDEO INFO 0 control register when set enables dithering during the vertical blanking interval. The initial condition of Dither Enable and V Dither Enable is OFF.

The **SMPTE scrambler** accepts 10-bit standard definition or 20-bit high definition parallel video data and encodes it using the polynomial  $X^9 + X^4 + 1$  as specified in the respective standard: SMPTE 259M, SMPTE 344M or SMPTE 292M. The data is then serialized and sent to the **NRZ-to-NRZI** converter before being output. The transmission bit order is LSB-first.

The NRZ-to-NRZI converter accepts NRZ serial data from the SMPTE scrambler. The data is converted to NRZI format using the polynomial (X+1). The converter's output goes to the output cable driver amplifier.

#### ANCILLARY/CONTROL DATA PATH

The 10-bit, bi-directional **Ancillary and Control Data Port** performs two distinct functions in the CLC030. First, it is used to selectively load ancillary data into the Ancillary Data FIFO for insertion into the video data stream. The utilization and flow of ancillary data within the device is managed by a system of control bits, masks and IDs in the control data registers. Second, this port provides read/write access to contents of the configuration and control registers.

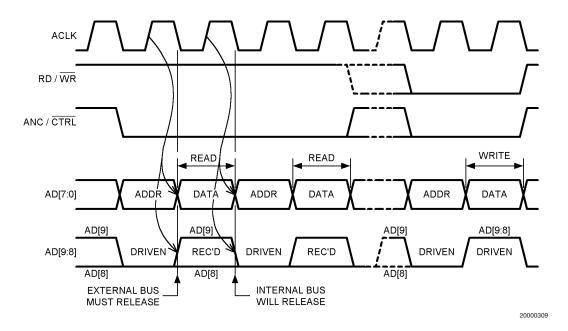

Ancillary and control data are input via the 10-bit Ancillary/ Control Data Port, AD[9:0]. The state of the RD/WR control input determines whether data is read or written to the registers or written to the Ancillary Data FIFO. The state of the ANC/CTRL control input selects which of the ancillary data or control data sub-systems is accessed through the port.

The ACLK input controls data flow through the port. The operation and frequency of ACLK is independent of the video data clock, VCLK. However, the frequency of ACLK must be less than or equal to VCLK. There is no low frequency limit for ACLK when it is being used for control register access. When the ANC/CTRL input is a logic-high, ACLK affects only the ancillary data FIFO operation. When the ANC/CTRL input is a logic-low, ACLK affects only the control register operation.

Inputs AD[9:0], RD/WR and ANC/CTRL have internal pull down devices. ACLK does not have an internal pull down device.

#### **CONTROL DATA READ FUNCTIONS**

Control data is written to and read from the CLC030 using the lower-order 8 bits AD[7:0] of the Ancillary/Control Data Port. This control data initializes, monitors and controls operation of the CLC030. The upper two bits AD[9:8] of the port are handshaking signals with the device accessing the port. AD[9:8] must be driven as 00b (0XXh, where XX are AD[7:0]) when either a control register read or write address is being written to the port. AD[9:8] must be driven as 11b (3XXh, where XX are AD[7:0]) when control data is being written to the port. When control data is being read from the port, the CLC030 will output AD[9:8] as 10b (2XXh, where XX are output data AD[7:0]) and may be ignored by the monitoring system.

**Note:** When power is first applied to the device or after it is reset, the **Ancillary and Control Data Port** must be initialized to receive data. This is done by toggling **ACLK** three (3) times.

Figure 1 shows the sequence of clock and control signals for reading control data from the ancillary/control data port. The

Control Data Read mode is entered by making the ANC/CTRL input low and the RD/WR input high. Next, the 8-bit address of the control register set to be accessed is placed on port bits AD[7:0]. When a control register read address is being written to the port, AD[9:8] must be driven as 00b (0XXh, where XX are AD[7:0]). ACLK is then toggled. The address is captured on the rising edge of ACLK. Observe the port input hold timing specification.

Data from the selected register is driven by the port within a few nanoseconds immediately following the rising edge of ACLK. To avoid contention with the port, the address driver should be turned off or tri-stated immediately after the address is clocked into the device. Data may be read by external devices at any time after the removal of the address signal. Output data will be driven until the next rising edge of ACLK. When the host system finishes reading the data, toggle ACLK again. This second clock resets the port from drive to receive mode and readies the port for another access cycle. When control data is being read from the port, the CLC030 will output AD[9:8] as 10b (2XXh, where XX are output data AD[7:0]) and may be ignored by the monitoring system.

Example: Read the Full-field Flags via the AD port.

- 1. Set ANC/CTRL to a logic-low.

- 2. Set RD/WR to a logic-high.

- 3. Present 001h to AD[9:0] as the register address.

- 4. Toggle ACLK.

- 5. Release the bus driving the AD port.

- Read the data present on the AD port. The Full-field Flags are bits AD[4:0].

- 7. Toggle ACLK to release the AD port.

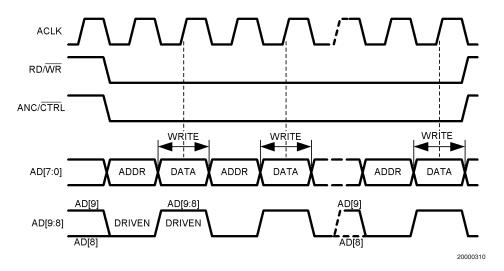

FIGURE 1. Control Data Read Timing (2 read and 1 write cycle shown)

#### **CONTROL DATA WRITE FUNCTIONS**

Figure 2 shows the sequence of clock and control signals for writing control data to the ancillary/control data port. The control data write mode is similar to the read mode. The control data write mode is started by making both the ANC/CTRL input low and the RD/WR input low. Next, the 8-bit address of the control register set to be accessed is placed on port bits AD[7:0]. When a control register write address is being written to the port, AD[9:8] must be driven as 00b (0XXh, where XX are AD[7:0]). Toggle ACLK. The address is captured on the rising edge of ACLK. Remove the address after clocking it into the device on or before the falling edge of ACLK. Observe the port input hold timing specification.

Next, the control register data is placed on the AD[7:0] port. ACLK is again toggled. The data is written to the selected register on the rising edge of ACLK. When control data is

being written to the port, **AD[9:8]** must be driven as 11b (3XXh, where XX are AD[7:0]). Remove the register data after clocking it into the device on or before the falling edge of **ACLK**. Observe the port input hold timing specification.

**Example:** Setup (without enabling) the TPG Mode via the AD port using the 1125 line, 30 frame, 74.25MHz, interlaced component (SMPTE 274M) color bars as test pattern. The TPG may be enabled after setup using the Multi-function I/O port or by the control registers.

- 1. Set ANC/CTRL to a logic-low.

- 2. Set RD/WR to a logic-low.

- 3. Present 00Dh to AD[9:0] as the Test 0 register address.

- Toggle ACLK.

- Present 327h to AD[9:0] as the register data.

- Toggle ACLK.

FIGURE 2. Control Data Write Timing

#### **ANCILLARY DATA FUNCTIONS**

The CLC030 can multiplex **Ancillary Data** into the serial component video data stream. The ancillary data packet structure, formatting and control words are given in standard SMPTE 291M. The data may reside in portions of the horizontal and vertical blanking intervals. The data can consist of different types of message packets including audio data. The CLC030 supports ancillary data in the HANC and VANC areas of standard definition component video and in the chrominance channel (C'r/C'b) only for high-definition operation. As it applies to embedded (multiplexed) audio data, this function follows the recommended practice for AES/EBU default Level A data handling.

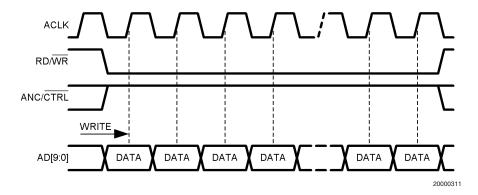

Figure 3 shows the sequence of clock, data and control signals for writing **Ancillary Data** to the port. In ancillary data write mode, 10-bit ancillary data is written into the **AD[9:0]** port and subsequently into the ancillary data FIFO. From the FIFO, the ancillary data can be inserted into the ancillary data areas in the serial video data stream. Ancillary data may be written to the FIFO only when in the ancillary data mode. Ancillary data cannot be read from the FIFO through the AD Port.

The process of loading ancillary data into the FIFO is done during the active video portion of the video line. Occurrence

of the active video line interval is indicated by the H-bit in the fourth word of the TRS sequence. The H-bit is available on I/O Port bit-2.

The ancillary data write process begins by making the ANC/ CTRL input high and the RD/WR input low. Next, the data words are presented to the port in sequence as specified in SMPTE 291M beginning with the DID word. Data presented to the port within the required setup and hold time parameters will be written into the FIFO on the rising edge of ACLK. The user has the option of including a checksum in the ANC input data or of having the CLC030 calculate and append the checksum. The CLC030 will append the Ancillary Data Flag to each packet automatically before multiplexing with the video data.

The process of writing ancillary data to the FIFO is effectively a double-buffered write operation. Therefore, in order to properly write the last word of the data packet, the CRC, whether supplied with the ANC data packet or internally generated, to the FIFO, **ACLK** must be toggled two additional times after the last data word is clocked into the port (or when the CRC is being generated internally and appended). In the case where multiple packets are being loaded to the FIFO, the additional clocks are issued after the last word of the final packet is received by the port.

Writing of ancillary data to the FIFO, packet handling and insertion into the video data stream are controlled by a

system of masking and control bits in the control registers. These and other ancillary data control functions such as **CHKSUM ATTACH IN** are explained in detail later in this data sheet.

FIGURE 3. Ancillary Data Write Timing

#### **MULTI-FUNCTION I/O PORT**

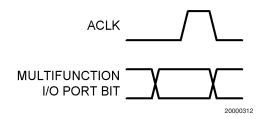

The **Multi-function I/O port** can be configured to provide immediate access to many control and indicator functions within the CLC030 configuration and control registers. The individual pins comprising this port may be assigned as input or output for selected bits in the control data registers. The multi-function I/O port is configured by way of an 8x6-bit register bank, **I/O pin 0 CONFIG** through **I/O pin 7 CONFIG**. The pin configuration registers contain codes which assign a control register bit to a particular I/O pin. Controls and indicators that are accessible by the port and their corresponding selection addresses are given in the I/O Pin Configuration Register Addresses, *Table 6. Table 2* gives the control register bit assignments.

**Caution:** When writing data into the control registers via the multi-function I/O port, **ACLK** must be toggled to register the data as shown in *Figure 4*. It is not necessary to toggle **ACLK** when reading data from the multi-function I/O port.

**Example:** Program multi-function I/O port bit-0 as the CRC Luma Error bit output.

- 1. Set ANC/CTRL to a logic-low.

- 2. Set RD/WR to a logic-low.

- Present 00Fh to AD[9:0] as the I/O PIN 0 CONFIG register address.

- 4. Toggle ACLK.

- 5. Present 310h to AD[9:0] as the register data.

- 6. Toggle ACLK.

FIGURE 4. I/O Port Data Write Timing

#### **EDH/CRC SYSTEM**

The CLC030 has EDH and CRC character generation and insertion circuitry. The EDH system functions as described in SMPTE Recommended Practice RP-165. The CRC system functions as specified in SMPTE 292M. The EDH/CRC polynomial generators accept parallel data from the input register and generate the EDH and CRC check words for insertion in the serial data. Incoming parallel data is checked for errors and the EDH flags are updated automatically. EDH check words and status flags for SDTV data are generated using the polynomial  $X^{16} + X^{12} + X^6 + 1$  per SMPTE RP165. EDH check words are inserted in the serial data stream at the correct positions in the ancillary data space and formatted per SMPTE 291M. Generation and automatic insertion of the EDH check words is controlled by EDH Force and EDH **Enable** bits in the control registers. After a reset, the initial state of all EDH and CRC check characters is 00h.

The SMPTE 292M high definition video standard employs **CRC** (cyclic redundancy check codes) error checking instead of EDH. The CRC consists of two 18-bit words generated using the polynomial  $X^{18} + X^5 + X^4 + 1$  per SMPTE 292M. One CRC is used for luminance and one for chrominance data. CRC data is inserted at the required place in the video data according to SMPTE 292M. The CRCs appear in the data stream following the EAV and line number characters

EDH and CRC errors are reported in the EDH0, EDH1, and EDH2 register sets of the configuration and control registers.

#### PHASE-LOCKED LOOP SYSTEM

The **phase-locked loop** (PLL) system generates the output serial data clock at 10x (standard definition) or 20x (high definition) the parallel data clock frequency. This system consists of a VCO, dividers, phase-frequency detector and internal loop filter. The VCO free-running frequency is internally set. The parallel data clock  $\mathbf{V_{CLK}}$  is the reference for the PLL. The PLL automatically generates the appropriate frequency for the serial clock rate. Loop filtering is internal to the CLC030. The VCO has separate analog and digital power supply feeds:  $\mathbf{V_{DDPLLA}}$  pin 62,  $\mathbf{V_{SSPLLA}}$  pin 61,  $\mathbf{V_{DDPLLD}}$  pin 1, and  $\mathbf{V_{SSPLLD}}$  pin 2. These may be separately

supplied power via external low-pass filters, if desired. PLL acquisition time is less than 200 $\mu$ s @ 1,485 Mbps. The VCO halts when the V<sub>CLK</sub> signal is not present or is inactive.

A LOCK DETECT indicator function is available as a bit in the VIDEO INFO 0 control registers. LOCK DETECT is a logic-1 when the PLL is locked and a valid format has been detected. It can be assigned as an output on the multifunction I/O port. By default LOCK DETECT is assigned as I/O Port bit 4 after power-on or reset . This function also includes logic to check the stability of the device after the digital logic reset is released following PLL lock. If the system is not fully stable, the logic is automatically reset. LOCK DETECT also combines the function of indicating that the CLC030 has detected the video format being received. This format detect function involves determination of the major raster parameters such as line length, number of video lines in a frame, and so forth. This is done so that information like line numbering can be correctly inserted. The PLL itself will have locked in 200 microseconds (HD rates) or less. However, resolution of all raster parameters may take the majority of a

#### **SERIAL DATA OUTPUT DRIVER**

The **serial data outputs** provide low-skew complimentary or differential signals. The output buffer is a current-mode design and is intended to drive AC-coupled and terminated,  $75\Omega$  coaxial cables. The driver automatically adjusts its output slew rate depending upon the data rate being processed. Output levels are  $800~\text{mV}_{\text{P-P}}$   $\pm 10\%$  into  $75\Omega$  AC-coupled loads. The  $75\Omega$  resistors connected to the SDO outputs function both as drain-load and back-matching resistors. Series back-matching resistors are not used with this output type.

The serial output level is controlled by the value of R<sub>BEE</sub>LVL and R<sub>BEF</sub>PRE connected to pin 53 and pin 52, respectively. The R<sub>BEE</sub>LVL resistor sets the peak-to-peak level of the output signal to the required SMPTE nominal level. The R<sub>BEE</sub>PRE resistor sets the value of a pre-emphasis current which is active during the transition times of the HD-rate output signal. The value of  $R_{\text{REF}}LVL$  is normally 4.75 K $\Omega$ ,  $\pm 1\%$ . The value of R<sub>BEF</sub>PRE is normally 4.75 K $\Omega$ ,  $\pm 1\%$ . The voltage present at these pins is approximately +1.3Vdc. The transition times of this output buffer design automatically adjust and are different for the HD and SD data rate conditions. The output buffer is quiescent when the device is in an out-of-lock condition. The output will become active after the PLL is locked and a valid format has been detected. Separate power feeds are provided for the serial output driver:  $V_{SSSD}$ , pins 54, 55, and 59;  $V_{DDSD}$ , pin 51; and  $V_{DDLS}$ , pin

**CAUTION:** This output buffer is not designed or specified for driving  $50\Omega$  or other impedance loads.

# POWER SUPPLIES, POWER-ON-RESET AND RESET INPUT

The CLC030 requires two power supplies, 2.5V for the core logic functions and 3.3V for the I/O functions. The supplies must be applied to the device in proper sequence. The 3.3V supply must be applied prior to or coincident with the 2.5V supply. Application of the 2.5V supply must not precede the 3.3V supply. It is recommended that the 3.3V supply be configured or designed so as to control application of the 2.5V supply in order to satisfy this sequencing requirement.

The CLC030 has an automatic, **power-on-reset** circuit. Reset initializes the device and clears TRS detection circuitry, all latches, registers, counters and polynomial generators, sets the EDH/CRC characters to 00h and disables the serial output. *Table 1* lists the initial conditions of the configuration and control registers. An active-HIGH-true, manual **reset input** is available at pin 64. The reset input has an internal pull-down device and may be considered inactive when unconnected

**Important:** When power is first applied to the device or following a reset, the **Ancillary and Control Data Port** must be initialized to receive data. This is done by toggling **ACLK** three times.

# TEST PATTERN GENERATOR (TPG) AND BUILT-IN SELF-TEST (BIST)

The CLC030 includes a built-in **test pattern generator (TPG)**. Four test pattern types are available for all data rates, all HD and SD formats, NTSC and PAL standards, and 4x3 and 16x9 raster sizes. The test patterns are: flat-field black, PLL pathological, equalizer (EQ) pathological and a 75%, 8-color vertical bar pattern. The pathologicals follow the recommendations of SMPTE RP 178-1996 regarding the test data used. The color bar pattern has optional bandwidth limiting coding in the chroma and luma data transitions between bars. The **VPG FILTER ENABLE** bit in the **VIDEO INFO 0** control register enables the color bar filter function. The default condition of **VPG FILTER ENABLE** is OFF.

The TPG also functions as a **built-in self-test (BIST)** which can verify device functionality. The BIST function performs a comprehensive go/no-go test of the device. The test may be run using any of the HD color bar test patterns or one of two SD test patterns, either a 270 Mb/s NTSC full-field color bar or a PAL PLL pathological, as the test data pattern. Data is supplied internally in the input data register, processed through the device and tested for errors using either the EDH system for SD or the CRC system for HD. A go/no-go indication is logged in the **Pass/Fail** bit of the **TEST 0** control register set. This bit may be assigned as an output on the multifunction I/O port.

TPG and BIST operation is initiated by loading the code for the desired test pattern into the Test Pattern Select [5:0] bits of the TEST 0 register. Table 5 gives the available test patterns and codes. (Recall also the requirement to initialize the ancillary data port control logic by clocking ACLK at least three (3) complete cycles before attempting to load the first register address). In the default power-on state, TPG Enable appears as bit 7 on the multi-function I/O port. The TPG is run by applying the appropriate frequency at the VCLK input for the format and rate selected and then setting the TPG Enable input on the multi-function I/O port, or by setting the TPG Enable bit in the TEST 0 register.

**Important:** If the **TPG Enable** input of the I/O port is in its default mapping and is not being used to enable the TPG mode, attempting to enable TPG operation by setting bit 6 of the **TEST 0** register will not cause the TPG to operate. This is because the low logic level at the I/O port input pulldown overrides the high level being written to the register. The result is the TPG does not run.

The Pass/Fail bit in the TEST 0 control register indicates the test status. If no errors have been detected, this bit will be set to logic-1 approximately 2 field intervals after TPG Enable is set. If errors have been detected in the internal circuitry of the CLC030, Pass/Fail will remain reset to a

logic-0. The TPG or BIST is halted by resetting **TPG Enable**. The serial output data is present at the SDO outputs during TPG or BIST operation.

Caution! When attempting to use the TPG or BIST immediately after applying power or resetting the device, the TPG defaults to the 270Mbps SD rate and expects a  $V_{\text{CLK}}$  clock frequency of 27MHz as input. This is because the code for the test pattern in the TEST 0 register is set to 00h (525 line, 30 frame, 27MHz, NTSC 4x3 reference black). Attempting to apply a V<sub>CLK</sub> frequency higher than the device expects, according to the setting in the TEST 0 register, may result in the PLL locking up while attempting to slew to its maximum possible frequency. This situation is not recoverable by the use of the device RESET input. To recover from this condition, power must be removed and re-applied to the device. Proper conditioning of the V<sub>CLK</sub> input, which does not have an internal pull down device, is mandatory to prevent admission of noise or unwanted signals at any time, especially during power-up or reset sequences. It is strongly recommended that V<sub>CLK</sub> not be applied until device initialization and configuration is completed.

**Example:** Enable the TPG Mode to use the NTSC 270Mbps color bars as the BIST and TPG pattern. Enable TPG operation using the I/O port.

- 1. Set ANC/CTRL to a logic-low.

- 2. Set RD/WR to a logic-low.

- Present 00Dh to AD[9:0] as the TEST 0 register address

- 4. Toggle ACLK.

- Present 303h to AD[9:0] as the register data (525 line, 30 frame, 27MHz, NTSC 4x3, color bars (SMPTE 125M)).

- 6. Toggle ACLK.

- 7. Set TPG ENABLE (I/O Port, bit 7) to a logic-high.

- 8. Toggle ACLK.

- The PASS/FAIL indicator (I/O Port, bit 6) is monitored for the result of the test. Alternatively, the TEST 0 register may be read. Bit 7 is the Pass/Fail indicator bit.

#### **CONFIGURATION AND CONTROL REGISTERS**

The configuration and control registers store data which configures the operational modes of the CLC030 or which result from its operation. Many of these registers can be mapped to the multi-function I/O bus to make them available as external I/O functions. These functions and initial values are summarized in *Table 1* and detailed in *Table 2*. The power-on default condition for the multi-function I/O port is indicated in *Table 1* and detailed in *Table 6*.

TABLE 1. Configuration and Control Data Register Summary

| Register Function       | Bits          | Read or Write | Initial Condition<br>(Note 12) | Assignable to I/O Bus as | Notes                |

|-------------------------|---------------|---------------|--------------------------------|--------------------------|----------------------|

| EDH Error (SD)          | 1             | R             |                                | Output                   | (Note 11)            |

| Full-Field Flags        | 5             | R             | Reset                          | No                       |                      |

| Active Picture Flags    | 5             | R             | Reset                          | No                       |                      |

| ANC Flags               | 5             | R             | Reset                          | No                       |                      |

| EDH Force               | 1             | R/W           | OFF                            | Input                    |                      |

| EDH Enable              | 1             | R/W           | ON                             | Input                    |                      |

| F/F Flag Error          | 1             | R             | Reset                          | Output                   |                      |

| A/P Flag Error          | 1             | R             | Reset                          | Output                   |                      |

| ANC Flag Error          | 1             | R             | Reset                          | Output                   |                      |

| ANC Checksum            | 1             | R/W           | OFF                            | Input                    |                      |

| Force                   |               |               |                                | ·                        |                      |

| ANC Checksum            | 1             | R             | Reset                          | Output                   |                      |

| Error                   |               |               |                                |                          |                      |

| FIFO Empty              | 1             | R             | Set                            | Output                   |                      |

| FIFO Full               | 1             | R             | Reset                          | Output                   |                      |

| FIFO Overrun            | 1             | R/W           | OFF                            | Input/Output             |                      |

| Video FIFO Depth        | 3             | R/W           | 000b                           | No                       |                      |

| ANC ID                  | 16            | R/W           | 0000h                          | No                       |                      |

| ANC Mask                | 16            | R/W           | FFFFh                          | No                       |                      |

| MSG Track               | 1             | R/W           | OFF                            | No                       |                      |

| MSG Flush Static        | 1             | R/W           | OFF                            | No                       |                      |

| MSG Flush Dynamic       | <br>1         | R/W           | OFF                            | No                       |                      |

| FIFO Flush Static       | <br>1         | R/W           | OFF                            | No                       |                      |

| FIFO Flush Dynamic      | <br>1         | R/W           | OFF                            | No                       |                      |

| MSG Flush Static        | <br>1         | R/W           | OFF                            | No                       |                      |

| Full MSG Required       | <br>1         | R/W           | OFF                            | No                       |                      |

| Chksum Attach In        | <u>·</u><br>1 | R/W           | OFF                            | Input                    |                      |

| FIFO Insert Enable      | 1             | R/W           | OFF                            | Input                    |                      |

| ANC Parity Mask         | <u>'</u><br>1 | R/W           | OFF                            | No                       |                      |

| Disable                 |               | 11/44         |                                | 140                      |                      |

| VANC                    | 1             | R/W           | OFF                            | No                       |                      |

| Switch Point 0          | 8             | R/W           | 00h                            | No                       |                      |

| Switch Point 1          | 8             | R/W           | 00h                            | No                       |                      |

| Switch Point 2          | 8             | R/W           | 00h                            | No                       |                      |

| Switch Point 3          | 8             | R/W           | 00h                            | No                       |                      |

| Format Set              | 5             | R/W           | OFF                            | No                       |                      |

| SD Only                 | 1             | R/W           | OFF                            | No                       |                      |

| HD Only                 | 1             | R/W           | OFF                            | No                       |                      |

| Format                  |               | R             | 011                            | Output                   | Format [4] (Note 11) |

| H                       | 1             | R             |                                | Output                   | (Note 11)            |

| V                       |               | R             |                                |                          | (Note 11)            |

| F                       | 1             |               |                                | Output                   |                      |

|                         | 1             | R             | 000006                         | Output                   | (Note 11)            |

| Test Pattern Select     | 6             | R/W           | 00000b                         | Input                    | 525/27 MHz/Black     |

| TPG Enable              | 1             | R/W           | OFF                            | Input                    | (Note 11)            |

| Pass/Fail               | 1             | R             |                                | Output                   | (Note 11)            |

| New Sync Position (NSP) | 1             | R             |                                | Output                   |                      |

TABLE 1. Configuration and Control Data Register Summary (Continued)

| Register Function   | Bits | Read or Write | Initial Condition<br>(Note 12) | Assignable to I/O Bus as | Notes     |

|---------------------|------|---------------|--------------------------------|--------------------------|-----------|

| SAV                 | 1    | R             |                                | Output                   |           |

| EAV                 | 1    | R             |                                | Output                   |           |

| Lock Detect         | 1    | R             |                                | Output                   | (Note 11) |

| VPG Filter Enable   | 1    | R/W           | OFF                            | Input                    |           |

| Dither_Enable       | 1    | R/W           | OFF                            | Input                    |           |

| Vert. Dither Enable | 1    | R/W           | OFF                            | No                       |           |

| Scrambler_ Enable   | 1    | R/W           | ON                             | No                       |           |

| NRZI_Enable         | 1    | R/W           | ON                             | No                       |           |

| LSB_Clipping        | 1    | R/W           | ON                             | No                       |           |

| SYNC_Detect_Enable  | 1    | R/W           | ON                             | No                       |           |

| I/O Bus Pin Config. | 48   | R/W           | See Table 6                    | No                       |           |

Note 11: Connected to multifunction I/O port at power-on.

Note 12: ON = logic-1, OFF = logic-0 (positive logic).

#### **TABLE 2. Control Register Bit Assignments**

|                   |                  | IADEL              | z. Control neg | ister bit Assign | 111101113    |              |              |

|-------------------|------------------|--------------------|----------------|------------------|--------------|--------------|--------------|

| Bit 7             | Bit 6            | Bit 5              | Bit 4          | Bit 3            | Bit 2        | Bit 1        | Bit 0        |

| EDH 0 (register   | r address 01h)   |                    |                |                  |              |              |              |

| EDH ERROR<br>(SD) | EDH FORCE        | EDH ENABLE         | F/F FLAGS(4)   | F/F FLAGS(3)     | F/F FLAGS(2) | F/F FLAGS(1) | F/F FLAGS(0) |

| EDH 1 (register   | r address 02h)   |                    |                |                  |              |              |              |

| reserved          | reserved         | reserved           | A/P FLAGS(4)   | A/P FLAGS(3)     | A/P FLAGS(2) | A/P FLAGS(1) | A/P FLAGS(0) |

| EDH 2 (register   | r address 03h)   |                    |                |                  |              |              |              |

| F/F FLAG          | A/P FLAG         | ANC FLAG           | ANC            | ANC              | ANC          | ANC          | ANC          |

| ERROR             | ERROR            | ERROR              | FLAGS(4)       | FLAGS(3)         | FLAGS(2)     | FLAGS(1)     | FLAGS(0)     |

| ANC 0 (registe    | r address 04h)   |                    |                |                  |              |              |              |

| VIDEO FIFO        | VIDEO FIFO       | VIDEO FIFO         | FIFO           | FIFO             | FIFO         | ANC CHECK-   | ANC CHECK-   |

| DEPTH(2)          | DEPTH(1)         | DEPTH(0)           | OVERRUN        | EMPTY            | FULL         | SUM ERROR    | SUM FORCE    |

| ANC 1 (registe    | r address 05h) l | DID                |                |                  |              |              |              |

| ANC ID(7)         | ANC ID(6)        | ANC ID(5)          | ANC ID(4)      | ANC ID(3)        | ANC ID(2)    | ANC ID(1)    | ANC ID(0)    |

| ANC 2 (registe    | r address 06h) 🤄 | SDID/DBN           |                |                  |              |              |              |

| ANC ID(15)        | ANC ID(14)       | ANC ID(13)         | ANC ID(12)     | ANC ID(11)       | ANC ID(10)   | ANC ID(9)    | ANC ID(8)    |

| ANC 3 (registe    | r address 07h) l | DID                |                |                  |              |              |              |

| ANC MASK(7)       | ANC MASK(6)      | ANC MASK(5)        | ANC MASK(4)    | ANC MASK(3)      | ANC MASK(2)  | ANC MASK(1)  | ANC MASK(0)  |

| ANC 4 (registe    | r address 08h)   | SDID/DBN           |                |                  |              |              |              |

| ANC               | ANC              | ANC                | ANC            | ANC              | ANC          | ANC MASK(9)  | ANC MASK(8)  |

| MASK(15)          | MASK(14)         | MASK(13)           | MASK(12)       | MASK(11)         | MASK(10)     | ANC MASK(9)  | ANC WASK(6)  |

| ANC 5 (registe    | r address 17h)   |                    |                |                  |              |              |              |

| FIFO INSERT       | CHKSUM           | FULL MSG           | FIFO FLUSH     | FIFO FLUSH       | MSG FLUSH    | MSG FLUSH    | MSG TRACK    |

| ENABLE            | ATTACH IN        | REQUIRED           | DYNAMIC        | STATIC           | DYNAMIC      | STATIC       | WISG THACK   |

| ANC 6 (registe    | r address 18h)   |                    |                |                  |              |              |              |

| reserved          | reserved         | ANC PARITY<br>MASK | reserved       | reserved         | reserved     | reserved     | VANC         |

| SWITCH POINT      | 0 (register add  | dress 09h)         |                |                  |              |              |              |

| LINE(7)           | LINE(6)          | LINE(5)            | LINE(4)        | LINE(3)          | LINE(2)      | LINE(1)      | LINE(0)      |

| SWITCH POINT      | 1 (register add  | dress 0Ah)         |                |                  |              |              |              |

| PROTECT(4)        | PROTECT(3)       | PROTECT(2)         | PROTECT(1)     | PROTECT(0)       | LINE(10)     | LINE(9)      | LINE(8)      |

| SWITCH POINT      | 2 (register add  | dress 19h)         |                |                  |              |              |              |

| LINE(7)           | LINE(6)          | LINE(5)            | LINE(4)        | LINE(3)          | LINE(2)      | LINE(1)      | LINE(0)      |

|                   |                  | •                  |                |                  |              |              |              |

#### **Device Operation** (Continued) TABLE 2. Control Register Bit Assignments (Continued) Bit 7 Bit 6 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 SWITCH POINT 3 (register address 1Ah) PROTECT(4) PROTECT(3) PROTECT(2) PROTECT(1) PROTECT(0) LINE(10) LINE(9) LINE(8) FORMAT 0 (register address 0Bh) **FORMAT FORMAT FORMAT FORMAT FORMAT** SD ONLY HD ONLY reserved SET(4) SET(2) SET(3) SET(1) SET(0) FORMAT 1 (register address 0Ch) Н FORMAT(4) FORMAT(3) FORMAT(2) FORMAT(1) FORMAT(0) TEST 0 (register address 0Dh) TEST TEST TEST **TEST** TEST TEST PASS/FAIL TPG ENABLE **PATTERN PATTERN PATTERN PATTERN PATTERN** PATTERN SELECT(5) SELECT(4) SELECT(3) SELECT(2) SELECT(1) SELECT(0) VIDEO INFO 0 (register address 0Eh) VERT. **DITHER** VPG FILTER LOCK **DITHER** EAV SAV NSP reserved **ENABLE ENABLE** DETECT **ENABLE MULTI-FUNCTION I/O BUS PIN CONFIGURATION** I/O PIN 0 CONFIG (register address 0Fh) PIN 0 SEL[0] reserved PIN 0 SEL[5] PIN 0 SEL[4] PIN 0 SEL[3] PIN 0 SEL[2] PIN 0 SEL[1] reserved I/O PIN 1 CONFIG (register address 10h) PIN 1 SEL[5] PIN 1 SEL[4] PIN 1 SEL[3] PIN 1 SEL[2] PIN 1 SEL[1] PIN 1 SEL[0] reserved reserved I/O PIN 2 CONFIG (register address 11h) PIN 2 SEL[5] reserved reserved PIN 2 SEL[4] PIN 2 SEL[3] PIN 2 SEL[2] PIN 2 SEL[1] PIN 2 SEL[0] I/O PIN 3 CONFIG (register address 12h) reserved reserved PIN 3 SEL[5] PIN 3 SEL[4] PIN 3 SEL[3] PIN 3 SEL[2] PIN 3 SEL[1] PIN 3 SEL[0] I/O PIN 4 CONFIG (register address 13h) PIN 4 SEL[5] PIN 4 SEL[3] PIN 4 SEL[2] reserved reserved PIN 4 SEL[4] PIN 4 SEL[1] PIN 4 SEL[0] I/P PIN 5 CONFIG (register address 14h) PIN 5 SEL[5] reserved reserved PIN 5 SEL[4] PIN 5 SEL[3] PIN 5 SEL[2] PIN 5 SEL[1] PIN 5 SEL[0] I/O PIN 6 CONFIG (register address 15h) reserved reserved PIN 6 SEL[5] PIN 6 SEL[4] PIN 6 SEL[3] PIN 6 SEL[2] PIN 6 SEL[1] PIN 6 SEL[0] I/O PIN 7 CONFIG (register address 16h) reserved reserved PIN 7 SEL[5] PIN 7 SEL[4] PIN 7 SEL[3] PIN 7 SEL[2] PIN 7 SEL[1] PIN 7 SEL[0] TEST MODE 0 (register address 55h) SYNC **SCRAMBLER** LSB reserved DETECT reserved NRZI ENABLE reserved reserved **CLIPPING ENABLE ENABLE**

**TABLE 3. Control Register Addresses**

| Posister Name         | Address | Address     |

|-----------------------|---------|-------------|

| Register Name         | Decimal | Hexadecimal |

| EDH 0                 | 1       | 01          |

| EDH 1                 | 2       | 02          |

| EDH 2                 | 3       | 03          |

| ANC 0                 | 4       | 04          |

| ANC 1                 | 5       | 05          |

| ANC 2                 | 6       | 06          |

| ANC 3                 | 7       | 07          |

| ANC 4                 | 8       | 08          |

| ANC 5                 | 23      | 17          |

| ANC 6                 | 24      | 18          |

| SWITCH POINT 0        | 9       | 09          |

| SWITCH POINT 1        | 10      | 0A          |

| SWITCH POINT 2        | 25      | 19          |

| SWITCH POINT 3        | 26      | 1A          |

| FORMAT 0              | 11      | 0B          |

| FORMAT 1              | 12      | 0C          |

| TEST 0                | 13      | 0D          |

| VIDEO INFO 0          | 14      | 0E          |

| I/O PIN 0             | 15      | 0F          |

| CONFIG                |         |             |

| I/O PIN 1             | 16      | 10          |

| CONFIG                |         |             |

| I/O PIN 2             | 17      | 11          |

| CONFIG                |         |             |

| I/O PIN 3             | 18      | 12          |

| CONFIG                |         |             |

| I/O PIN 4             | 19      | 13          |

| CONFIG                |         |             |

| I/O PIN 5             | 20      | 14          |

| CONFIG                | 0.4     | 4-          |

| I/O PIN 6             | 21      | 15          |

| CONFIG                | 00      | 10          |

| I/O PIN 7             | 22      | 16          |

| CONFIG<br>TEST MODE 0 | 85      | 55          |

| TEST MODE 0           | 00      | 55          |

# EDH REGISTERS 0, 1 AND 2 (Addresses 01h through 03h)

Updated EDH packets may be inserted into the serial output data by setting the **EDH Force** bit in the control registers. The **EDH Force** control bit causes the insertion of new EDH checkwords and flags into the serial output regardless of the previous condition of EDH checkwords and flags in the input parallel data. This function may be used in situations where video content has been editted thus making the previous EDH information invalid. In the case of SMPTE 292M data, the CRC check characters are recalculated and inserted automatically regardless of the presence of CRC characters in the parallel data. After the CLC030 is reset, the initial state of the CRC check characters is 00h.

The **EDH Enable** bit enables operation of the EDH generator function.

The **EDH ERROR (SD)** bit when set indicates that EDH error conditions are being reported in EDH ancillary data packets present in the parallel input data. Details of the specific error conditions contained in the EDH packets are reported via the full field, active picture and ancillary flag error bits and the specific flag bits in these registers.

The EDH flags F/F FLAGS[4:0] (full field), A/P FLAGS[4:0] (active picture) and ANC FLAGS[4:0] (ancillary data) are defined in SMPTE RP 165. The EDH flags are stored in the control registers. The flags are updated automatically when the EDH function is enabled and data is being received. The error flags indicate that error conditions were previously detected and reported via the EDH ancillary data packets in the parallel input data.

The status of EDH flag errors in incoming SD parallel data are reported in the ffFlagError, apFlagError and anc-FlagError bits. The ffFlagError, apFlagError and anc-FlagError bits are the logical-OR of the corresponding EDH and EDA flags of the EDH checkwords.

#### ANC REGISTER 0 (Address 04h)

The **V FIFO Depth[2:0]** bits control the depth of the video FIFO which follows the input data latches. The depth can be set from 0 to 4 stages deep by writing the corresponding binary code into these bits. For example: to set the Video FIFO depth at two registers, load 11010XXXXXb into the ANC 0 control register (where X represents the other functional bits of this register). To retain other data previously stored in a register, read the register's contents and logically-OR this with the new data. Then write the composite data back into the register.

Flags for FIFO EMPTY, FIFO FULL and FIFO OVERRUN are available in the configuration and control register set. These flags can also be assigned as inputs and outputs on the multi-function I/O port. The FIFO OVERRUN flag indicates that an attempt to write data into a full FIFO has occurred. When FIFO FLUSH DYNAMIC or MSG FLUSH DYNAMIC are enabled, the FIFO OVERRUN function is superceded. When FIFO OVERRUN is active and not superceded, it can be reset by reading the bit's status via the ancillary/Command port. To be used properly, FIFO OVERRUN should be assigned as an output on the multi-function I/O port and monitored by the host system. Otherwise, inadvertent loss of ancillary packet data could occur.

The ANC Checksum Force bit, under certain conditions, enables the overwriting of ancillary data checksums received in the parallel ancillary data. Calculation and insertion of new ancillary data checksums is controlled by the ANC Checksum Force bit. If a checksum error is detected (calculated and received checksums do not match) and the ANC Checksum Force bit is set, a new checksum will be inserted in the ancillary data replacing the previous one. If a checksum error is detected and the ANC Checksum Force bit is not set, the checksum mismatch is reported via the ANC Checksum Error bit.

Ancillary data checksums may be received in the incoming parallel ancillary data. Alternatively they may be calculated and inserted automatically by the CLC030. The CHKSUM ATTACH IN bit in the control registers when set to a logic-1 indicates that the checksum is to be supplied in the incoming data. When the CHKSUM ATTACH IN bit is set, checksums for incoming data are calculated and checked against received checksums. Calculation and insertion of new ancillary data checksum is controlled by the ANC Checksum Force

bit in the configuration and control registers. If a checksum error is detected (calculated and received checksums do not match) and the ANC Checksum Force bit is set, a new checksum will be inserted in the ancillary data replacing the previous one. If a checksum error is detected and the ANC Checksum Force bit is not set, the checksum mismatch is reported via the ANC CHECKSUM ERROR bit in the control registers.

The ANC Checksum Error bit indicates that the received ancillary data checksum did not agree with the CLC030's internally generated checksum. This bit is available as an output on the multifunction I/O port.

# ANC REGISTERS 1 THROUGH 4 (Address 05h through 08h)

Admission of ancillary data packets into the FIFO can be controlled by the ANC MASK[15:0] and ANC ID[15:0] bits in the control registers. The ANC ID[7:0] register can be set to a valid 8-bit Data Identification (DID) code used for component ancillary data packet identification as specified in SMPTE 291M. Similarly, the ANC ID[15:8] register can be set to a valid 8-bit Secondary Data Identification (SDID) or Data Block Number (DBN) code. The ANC MASK[7:0] is an 8-bit word that can be used to selectively control loading of packets with specific DIDs (or DID ranges) into the FIFO. Similarly, the ANC MASK[15:8] is an 8-bit word that can be used to selectively control loading of packets with specific SDID or DBNs (or SDID or DBN ranges).

When ANC MASK[7:0] or ANC MASK[15:8] is set to FFh, packets with any DID, SDID or DBN can be loaded into the FIFO. When any bit or bits of ANC MASK[7:0] or ANC MASK[15:8] are set to a logic-1, the corresponding bit or bits of ANC ID[7:0] or ANC ID[15:8], respectively are a don't-care when matching IDs of incoming packets. When ANC MASK[7:0] or ANC MASK[15:8] is set to 00h, the DID, SDID or DBN of incoming packets must match exactly, bit-for-bit, the setting of ANC ID[7:0] or ANC ID[15:8] in the control register for the packets to be loaded into the FIFO. The initial value of ANC MASK[7:0] and ANC MASK[15:8] is FFh. The initial value of ANC ID[7:0] and ANC ID[15:8] is 00h.

Bits 7 through 0 of Register ANC 1, **ANC ID[7:0]**, and Register ANC3, **ANC MASK[7:0]**, affect DID[7:0]. Bits 7 through 0 of Register ANC2, **ANC ID[15:8]**, and Register ANC 4, **ANC MASK[15:8]**, affect SDID[7:0] or DBN[7:0].

#### **ANC REGISTER 5 (Address 17h)**

The **FIFO INSERT ENABLE** bit enables insertion of ancillary data stored in the FIFO into the serial data stream. Data insertion is enabled when this bit is set to a logic-1. This bit can be used to delay automatic insertion of data into the serial data stream.

The CLC030 can keep track of up to 8 ancillary packets in the FIFO. Incoming packet length versus available space in the FIFO is also tracked. The MSG TRACK bit in the control registers, when set, enables tracking of packets in the FIFO. MSG TRACK also enables other functions for control of packet traffic in the FIFO: FIFO FLUSH DYN and MSG FLUSH DYN.

With message tracking enabled and FIFO FLUSH DYN set to a logic-1, if a FIFO full condition is encountered when attempting to load a packet, all existing message packets in the FIFO will be flushed. The current message packet will be left intact. When FIFO FLUSH DYN is not set and a FIFO full

condition is encountered, the FIFO will overrun and the FIFO OVERRUN flag will be set. FIFO FLUSH DYN remains set until cleared.

Setting the FIFO FLUSH STAT bit to a logic-1 flushes the FIFO. Data may not be loaded into the FIFO during FIFO FLUSH STAT execution. Similarly, FIFO FLUSH STAT may not be set when data is being input to the FIFO. FIFO FLUSH STAT is automatically reset after this operation is complete.

With message tracking enabled and MSG FLUSH DYN set to a logic-1, the oldest message packet in the FIFO will be flushed when the next message is written to the FIFO. MSG FLUSH DYN remains set until cleared.

When **MSG FLUSH STAT** is set to a logic-1, the oldest message packet in the FIFO is flushed when data is not being written to the FIFO. **MSG FLUSH STAT** is automatically reset after this operation is complete.

The **FULL MSG REQ** (full message required) bit in the control registers, when set, instructs the CLC030 to insert only complete packets residing in the FIFO into the serial data stream. When this bit is not set, incomplete or partial messages of any length up to the maximum buffer length will be inserted into the serial data stream. This function is not affected by **MSG TRACK**. This function can be used to prevent overrunning available space in the FIFO.

Execution of these FIFO operations requires toggling of  ${\bf ACLK}.$

#### **ANC REGISTER 6 (Addresses 18h)**

The **ANC PARITY MASK** bit when set disables parity checking for the DATA ID (DID) and SECONDARY DATA ID (SDID) or Data Block Number (DBN) in the ANC data packet. When reset, parity checking is enabled, and, if a parity error occurs, the packet will not be loaded.

The **VANC** bit in the control registers, when set to a logic-1, enables insertion of ancillary data during the vertical blanking interval.

# SWITCH POINT REGISTERS 0 THROUGH 3 (Addresses 09h, 0Ah, 19h and 1Ah)

The Line[10:0] and Protect[4:0] bits define the vertical switching point line and number of protected lines following the switching point line for fields 0 and 1 (or fields 1 and 2 as these are sometimes referred to) of high-defination formats. The vertical switching point for component digital standard definition formats is defined in SMPTE RP 168-1993. The vertical switching point for high-definition formats has the same basic definition. However, since the vertical switching point lines are not necessarily standardized among the various high-definition rasters, these registers provide a convenient means whereby the vertical switching point line and subsequent protected lines may be specified by the user. The Switch Point registers do not operate for standard definition formats.

The Line[10:0] bits of registers Switch Point 0 and 1 may be loaded with a line number ranging from 0 to 1023 which then specifies the switching point line for Field 0. The Protect[4:0] bits of register Switch Point 1 determine the number of lines from 0 to 15 after the vertical switching point line in which ancillary data may not be inserted. LINE(0) is the LSB and LINE(10) is the MSB for the Line[10:0] bits. Similar ordering holds for the Protect[4:0] bits.

The Line[10:0] and Protect[4:0] bits of registers Switch Point 2 and 3 perform the same function as explained above for the vertical switching point line for Field 1.

#### FORMAT REGISTERS 0 (Addresses 0Bh)

The CLC030 may be set to process a single video format by writing the appropriate data into the **FORMAT 0** register. The **Format Set[4:0]** bits confine the CLC030 to recognize and process only one of the fourteen specified types of standard or high definition formats. When the CLC030 is set to process a single format, it will not recognize and therefore will not process other formats that it is capable of recognizing. The **Format Set[4:0]** bits may not be used to confine device operation to a range of standards. For normal operating situations, it is recommended that the CLC030 be operated in automatic format detection mode, i.e. that the Format 0 register be set to 00h.

The available formats and codes are detailed in *Table 4*. Generally speaking, the **Format Set[4:0]** codes indicate or group the formats as follows: **Format Set[4]** is set for the HD formats and reset for the SD formats. **Format Set[3]** when

set indicates that PAL data is being processed. When reset NTSC data is being processed. **Format Set[2:0]** correspond to one of the sub-standards given in the table. Note that the CLC030 makes no distinction in formats resulting from the processing of data at 74.25MHz or 74.176MHz.

The **HD Only** bit when set to a logic-1 locks the CLC030 into the high definition data range and frequency. In systems designed to handle only high definition signals, enabling **HD Only** reduces the time required for the CLC030 to establish frequency lock and determine the HD format being processed

The **SD Only** bit when set to a logic-1 locks the CLC030 into the standard definition data ranges and frequencies. In systems designed to handle only standard definition signals, enabling **SD Only** reduces the time required for the CLC030 to establish frequency lock and determine the format being processed. When **SD Only** and **HD Only** are set to logic-0, the device operates in SD/HD mode.

**TABLE 4. Video Raster Format Parameters**